## Fiesta® POS-PHYL3 Peripheral Model

## **Features**

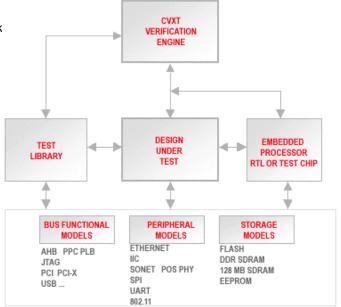

- Interfaces with Comit Fiesta® CVXT Open Verification Environment

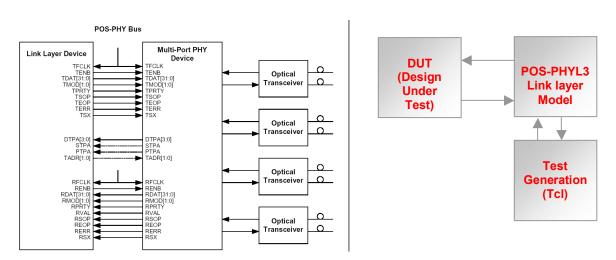

- Configures POS-PHY Layer 3 protocol for Link Layer Device

- Sideband signals control model behavior to simulate different conditions

- Number of ports: 1 to 48 links

- Data bits width: 8 or 32 bits

- Descriptors to set the following:

- Packet mode or Byte mode

- Packet size up to 512 bytes

- Packet Buffer Size

- Inter Packet Gap

- o Parity Error Control

- Packet Flow Pausing

- Sideband signals

- Transmit Base Address

- o Receive Base Address

- o Pulsed 'Sent Packet' indicator

- Sent Packet Address

- o Pulsed 'Received Packet' indicator

- o Pulsed 'Packet Stored' indicator

- Stored Packet Address

- Pulsed 'Packet Error' indicator

## **System Interface Diagram**

Fiesta® Process Standardization and Acceleration Tool Kit is an industrial strength suite of tools designed, developed, tested and used by engineers of Comit's Contract Engineering Center. Their experience in developing processes and methodology that yield predictable and accurate results forms the foundation of the toolkit. Use it with confidence.

<sup>©</sup> Copyright Comit Systems, Inc. Fiesta is a registered trademark of Comit Systems, Inc. CWGT, CRST, CSMT, CVXT, CMMT, CSGT, CAVT and CACT are trademarks of Comit Systems, Inc. Verilog is a registered trademark of Cadence Design Systems, Inc. All other trademarks property of their respective holders.