## Fiesta<sup>®</sup> FLASH Memory Model

## Features

- One 8K word, two 4K words, one 16K word, and thirty-one 32K words sectors in word mode

- One 16K byte, two 8K bytes, one 32K byte, and thirty-one 64K bytes sectors in byte mode

- Boot Code Sector Architecture

- T = Top sector

- B = Bottom sector

- Embedded Erase Algorithms

- Automatically pre-programs and erases the chip or any sector

- Embedded Program Algorithms

- Automatically programs and verifies data at specified address

- Data Polling and Toggle Bit feature for detection of program or erase cycle completion

- Ready/Busy output (RY/BY)

- Erase Suspend/Resume

- Suspends the erase operation to allow a read data and/or program in another sector within the same device

- Resets internal state machine to the read mode

- Sector protection disables any combination of sectors from program or erase operations

- Temporary sector unprotection

## System Interface Diagram

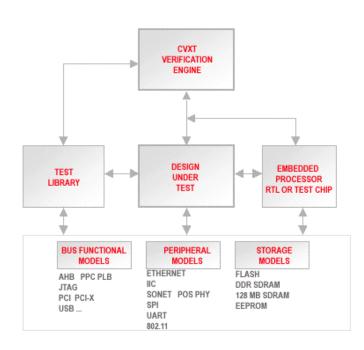

Fiesta<sup>®</sup> Process Standardization and Acceleration Tool Kit is an industrial strength suite of tools designed, developed, tested and used by engineers of Comit's Contract Engineering Center. Their experience in developing processes and methodology that yield predictable and accurate results forms the foundation of the toolkit. Use it with confidence.

© Copyright Comit Systems, Inc. Fiesta is a registered trademark of Comit Systems, Inc. CWGT, CRST, CSMT, CVXT, CMMT, CSGT, CAVT and CACT are trademarks of Comit Systems, Inc. Verilog is a registered trademark of Cadence Design Systems, Inc. All other trademarks property of their respective holders.

Comit Systems, Inc. 3375 Scott Blvd. Ste 139, Santa Clara, CA 95054. (408) 988 2988. www.comit.com